Intel’s next mobile architecture, Panther Lake, is slowly moving from slide decks and roadmaps into the real world. The latest clue comes from an engineering sample of a Panther Lake “Core Ultra Series 3” processor that has surfaced on Intel’s internal Reference Validation Platform (RVP) and in early CPU-Z tests.

While retail chips aren’t expected until around CES 2026, this ES chip already tells us a lot about how Intel plans to balance performance, efficiency, and integrated graphics in its next wave of thin-and-light laptops.

Early engineering silicon with an unusual 10-core layout

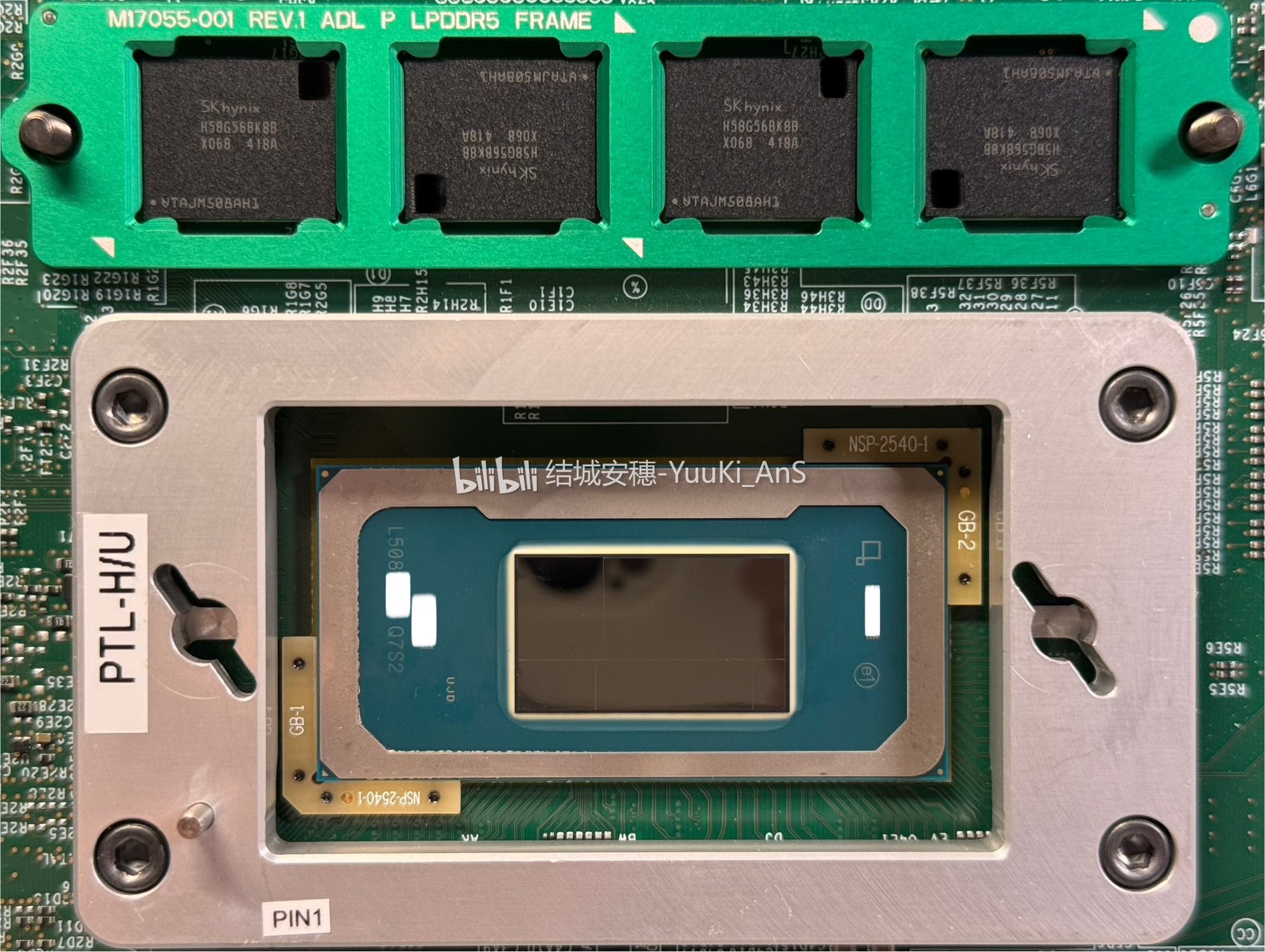

The sample in question is based on the PTL 16C/4Xe3 die and carries the device ID “000C06C0”. Physically, the package uses a BGA 2540 footprint with four active tiles and one filler tile on the SoC, showing once again how aggressively Intel is leaning into a tiled design for mobile. What makes this chip really interesting, however, is its 10-core configuration: 2 performance cores (P-cores), 4 efficiency cores (E-cores), and 4 low-power efficiency (LP-E) cores. In other words, it combines three different core types in a compact 25 W envelope, a clear sign that Intel is trying to squeeze every drop of efficiency out of its architecture.

This layout doesn’t match any of the leaked retail Panther Lake SKUs, where we mainly see higher-end H-series parts with more cores and beefier Xe3 iGPUs. That strongly suggests this is an internal test configuration or a future Core Ultra 5 or Core Ultra 3 U-class variant rather than a final flagship. Engineering samples often ship with odd core counts and disabled blocks, so the goal here is likely validation rather than headline-grabbing performance numbers.

Reference platform, memory configuration, and LPDDR5X details

The ES chip was tested on Intel’s own RVP platform, the same family of boards journalists briefly saw during Intel’s Tech Tour 2025. This reference board is built to abuse new silicon: it exposes every voltage rail and sensor, and it supports both modern LPCAMM2 modules and standard LPDDR5X soldered memory. For this particular sample, Intel went with 16 GB of LPDDR5X assembled in an Alder Lake (ADL-P) style frame using four SK hynix H58G56BK8BX068-418A DRAM packages.

The memory is running at 7467 MHz (effective), which is notably below the 9600 MT/s speeds Intel is targeting for finalized Panther Lake “Core Ultra Series 3” laptops. Notebook vendors are already experimenting with data rates north of 10 GT/s, so these conservative clocks are exactly what you’d expect from early silicon where stability matters more than raw bandwidth. Still, even at 7467 MT/s, we’re looking at a substantial jump over older LPDDR4X platforms, especially in bandwidth-hungry scenarios like integrated graphics gaming or AI workloads that lean heavily on memory throughput.

Clocks, caches, and power limits: a 25 W Panther Lake-U

On the CPU side, this Panther Lake ES part comes with 11 MB of L2 cache and 12 MB of L3 cache, feeding those 10 mixed cores. Base clock is set at 3.0 GHz with a modest 3.2 GHz boost, while the P-cores can sustain up to 3.0 GHz across all cores and the E-cores top out around 2.6 GHz under load. The 4 Xe3 integrated GPU cores sit on the same package, tied into the system through a 2.5 GT/s link, and are meant to scale much higher in shipping products, especially on H-series dies with up to 12 Xe3 clusters.

Crucially, this chip is tagged as a 25 W “Panther Lake-U” SKU. Its PL1 (long-term) power limit is 25 W, PL2 (short-term turbo) is 65 W, and PL4 peaks at a hefty 160 W with a maximum junction temperature of 100 °C. That power profile lines up with modern premium ultrabooks: a fairly relaxed 25 W sustained target for quiet operation and battery life, with the option to spike aggressively for short bursts. Critics in the enthusiast community are quick to point out that “max clocks” on modern laptop CPUs are often reachable for only a few seconds under heavy workloads, and this chip won’t change that physics. But the real story for mobile is how long the processor can sit near its PL1 without throttling, not how high the marketing boost clock goes.

Early CPU-Z benchmarks: underwhelming by design

The engineering sample has already been run through CPU-Z’s single-threaded and multi-threaded tests, and, predictably, the scores are nothing to write home about. Some commenters bluntly label the chip “DOA” and joke that Intel’s roadmap of “five nodes in four years” has turned into “no IPC gains in five years.” Others post charts comparing Intel’s process technology to TSMC’s 3 nm nodes and argue that the supposed “superior node” clearly isn’t translating into dominant clocks or efficiency.

That frustration is understandable if you only look at point-in-time scores, but it misses context. This is A0 stepping silicon with immature firmware, conservative clocks, and relatively slow memory for the platform. Historically, Intel’s ES chips can land far below final retail performance once microcode, clocks, and power policies are tuned. There’s also the simple fact that this is a U-class part aimed at 25 W ultrabooks, not a halo desktop chip meant to crush benchmark charts at any cost. Judging the whole Panther Lake family off this one early sample is like reviewing a car based on a prototype mule with half its systems disabled.

Where this ES sample fits in the wider Panther Lake lineup

Recent leaks outline a fairly crowded Panther Lake stack, with Core Ultra X9 and X7 H-series chips offering up to 8 P-cores, 8 E-cores and 12 Xe3 iGPU cores at 25 W with 65–80 W turbo limits, plus a spread of Core Ultra 7 and Ultra 5 parts with different core mixes and GPU counts. Notably, none of those rumored SKUs show the exact 2P + 4E + 4 LP-E configuration we see here. That reinforces the idea that this 10-core part is either a lab mule used to validate the 16C/4Xe3 die or an early look at an as-yet-unannounced Core Ultra 5 or Core Ultra 3 for thin-and-light designs.

If it does become a commercial product, it would sit below the H-series monsters but still above fanless designs, appealing to laptops that prioritize battery life and portability while still offering a modern Xe3 iGPU and decent multithreaded grunt. Think premium ultraportables rather than gaming rigs. And for OEMs, the combination of three core classes plus fast LPDDR5X and advanced power tuning could make it easier to build machines that feel snappy on the desktop without roaring like a jet engine under sustained load.

Community reaction: regression fears vs laptop reality

The reaction from enthusiasts so far has been sharply polarized. On one side, there are users insisting that “Intel is progressing only backwards,” claiming that the company will still be trying to catch up to AMD’s Strix Halo APUs by 2030 at this pace. Some mock the supposedly impressive node progress while pointing to real-world charts that show only modest generational gains and degrading performance between benchmark runs. Others roll their eyes at yet another mobile part with restrained frequencies, joking that even the efficiency cores feel slow compared to what they expected.

On the other side, a quieter but more pragmatic group points out that this is, after all, a laptop SKU. At 25 W, nobody sane wants a chip that cooks the chassis or dumps desktop-class power into a thin-and-light notebook. For that audience, consistent performance within a tight power budget, solid integrated graphics, and improved battery life are far more important than 5.5 GHz screenshots. Add Linux support and robust drivers into the mix and Panther Lake-U could still end up as a very compelling platform, even if it never tops the benchmark leaderboards.

What to watch as Panther Lake moves toward launch

For now, this early 10-core Panther Lake ES chip is best viewed as a teaser. It confirms the presence of triple-tier core configurations, tile-based packages, LPDDR5X support that will stretch toward 9600 MT/s and beyond, and Xe3 graphics even on modest U-series parts. It also highlights the tightrope Intel must walk: enthusiasts want big IPC and frequency jumps to justify the company’s aggressive “five nodes in four years” messaging, while laptop buyers and OEMs care more about efficiency, thermals, and sustained responsiveness.

As we get closer to CES 2026 and the official “Core Ultra Series 3” launch, the real questions will be how much single-threaded performance Panther Lake adds over today’s Core Ultra chips, how strong the Xe3 iGPU is against AMD’s next-gen APUs, and whether Intel can finally deliver not just promising slides but consistently strong real-world results. Until then, leaks like this engineering sample are useful not as final verdicts, but as early markers of where Intel’s mobile strategy is headed.

2 comments

People calling it DOA trash but this is literally an A0 ES laptop chip, calm down a bit

Intel: regress inside 😂 those charts vs tsmc 3nm look brutal ngl