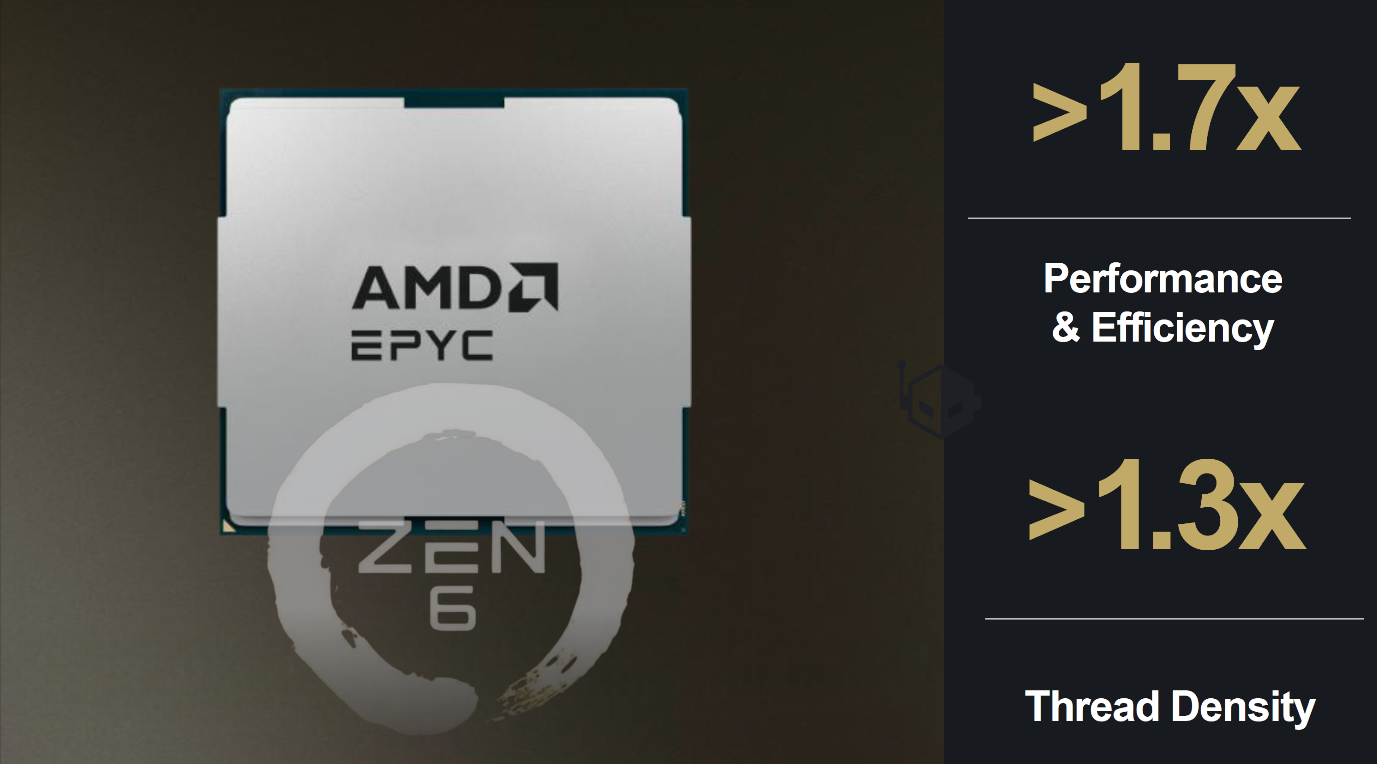

AMD is already looking beyond today’s Zen 5 launch window and talking publicly about what comes next. At its latest Financial Analyst Day, the company quietly dropped one of the boldest claims we have heard from it in years: the first EPYC processors based on the Zen 6 architecture, code-named “Venice”, are projected to deliver more than 70% combined performance and efficiency gains over today’s Zen 5 “Turin” chips in servers.

If those figures hold once silicon ships, the balance of power in the data center could tilt even further in AMD’s favor.

The slide AMD showed to investors focused on EPYC, but the implications spill far beyond the server rack. Zen 6 is a foundational core that will power not only EPYC Venice but also future desktop and mobile processors such as the Olympic Ridge platform for high-end PCs and the Medusa and Gator families for laptops. In other words, what AMD is building for hyperscalers today is a preview of what enthusiasts and everyday users may see on their desks a little further down the road.

EPYC Venice: up to 256 Zen 6 cores and denser threading

The raw core and thread numbers are the easiest part of the story to understand. AMD has already confirmed that top-end EPYC Venice processors will scale up to 256 cores and 512 threads in a single socket, compared with a maximum of 192 cores and 384 threads for the current Turin generation. That is roughly a 33% jump in core resources before we even talk about microarchitectural changes. On top of that, AMD is promising more than 30% higher thread density, meaning it can pack significantly more compute into the same physical footprint.

Core counts on their own do not tell the whole story, though. A good chunk of the projected >70% uplift still has to come from the Zen 6 core itself. Expect changes in IPC, cache hierarchy, memory subsystem behavior, interconnect bandwidth, and power management – all the invisible plumbing that lets those 256 cores stay busy instead of waiting on data. Client versions of Zen 6 are also expected to move to a 12-core CCD layout, up from 8 cores per CCD today, allowing mainstream Ryzen chips at the high end to reach up to 24 cores without turning into unwieldy multi-chip monsters.

Built on TSMC’s 2 nm GAA process

Underneath Zen 6 is another major transition: AMD will move its leading-edge products to TSMC’s 2 nm node, which switches from classical FinFETs to nanosheet gate-all-around transistors. This process is advertised as delivering around 10–15% higher performance at the same power envelope, or 25–30% lower power at a given performance target, plus roughly 15% better transistor density versus the current cutting-edge nodes. Those characteristics line up neatly with AMD’s promises around efficiency, especially in a world where data-center operators care as much about electricity bills and cooling as they do about raw benchmark scores.

For EPYC Venice, the mix of a denser node and architectural tightening should translate into more work per watt, more work per rack unit, and ultimately lower total cost of ownership for cloud providers. For client chips, the same ingredients can be traded in different ways: thinner laptops that still hold boost clocks longer, desktop rigs that run quieter, or high-end workstations that squeeze extra cores into the same thermal budget.

Where the >70% uplift really comes from

It is tempting to assume that AMD is leaning on AI benchmarks to reach that big headline number, especially in 2025 when every vendor wants to talk about accelerators. In reality, AMD explicitly based its internal comparison on SPECrate 2017 integer throughput runs. The company compared a two-socket platform with a pair of top-bin 6th Gen EPYC Venice CPUs to a two-socket system with its best 5th Gen EPYC Turin chips. The uplift figure is a blend of traditional performance and efficiency metrics rather than some cherry-picked neural-network showcase.

Even so, these are still internal projections dated late October 2025, not final retail measurements, and AMD is careful to say they are subject to change as silicon matures. Historically, however, the company’s long-range EPYC guidance has been more conservative than not. Zen 2, Zen 3, and Zen 4 all arrived close to their promised performance-per-watt trajectories, which is why many analysts take this new slide as a credible – if ambitious – signal of where Zen 6 is heading.

Gamers may shrug, but the server wins matter

Whenever AMD talks about giant core counts and enterprise benchmarks, part of the gaming crowd instinctively tunes out. You can already see the attitude in some online threads: people bluntly saying they do not care about another EPYC launch and asking why anyone would get excited about a chip that will never end up in their gaming rig. That reaction misses an important point. The reason AMD can afford to keep competing with Intel and, increasingly, with Nvidia in the broader data-center stack is precisely because server parts like Venice push margins and market share higher.

Nothing about a stronger EPYC roadmap is good news for Jensen Huang and the rest of Nvidia’s leadership team. CPUs still sit at the heart of every AI cluster, no matter how many GPUs you bolt on. If AMD can offer cloud providers a platform where Zen 6 CPUs, Instinct accelerators, and ROCm software come as a tightly integrated package, it suddenly becomes far easier for big customers to diversify away from Nvidia-only deployments. That leverage starts with boring-sounding metrics such as “SPECrate 2017 INT per watt” but ends with strategic decisions about who gets the next multi-billion-dollar data-center build-out.

Toward 50% server share and beyond

AMD has been open about its long-term ambition to claim more than half of the x86 server market. Zen 6-based EPYC Venice is the next major step on that journey, and Zen 7 is already visible further down the roadmap as the architecture that will have to sustain that momentum. If Venice really can deliver over 70% combined performance and efficiency gains in realistic multi-socket deployments, the argument for sticking with legacy platforms becomes weaker for every cloud and enterprise buyer still on the fence.

For now, AMD is keeping detailed Zen 6 specs under wraps, choosing to drip-feed high-level metrics instead of full block diagrams. But the message behind the marketing is clear: higher core counts, a cutting-edge 2 nm GAA process, and a sharpened Zen 6 core are all converging to make EPYC Venice a potentially disruptive product. Whether you are a data-center architect counting watts, a workstation user eyeing next-gen Ryzen, or a skeptical gamer posting memes about not caring, Zen 6 is likely to shape the hardware landscape you rely on over the next several years.

3 comments

All I see is lower power bills for DCs and maybe quieter laptops for us later, so yeah this actually matters 👀

Internal numbers again… I wanna see real world cloud workloads before crowning Venice king of servers

If you dont care why you even reading an article about EPYC lol